# Refresher® on COMPUTER ORGANIZATION &

# ARCHITECTURE

(BTES-401) P.T.U (BCSES1-401) M.R.S.P.T.U

WITH UPTO-DATE PREVIOUS QUESTION PAPERS CHAPTERWISE & LORDS MODEL TEST PAPERS (UNSOLVED)

B.E., B.Tech (P.T.U/M.R.S.P.T.U)

4th Semester (Computer Science Engg.)

**New Edition February 2020**

By

Ms. POOJA CHOPRA

MCA, M.Phil

Asst. Prof. in (CSE & IT)

DIPS Institute of Management & Technology

Jalandhar City.

# LORDS PUBLICATIONS (Regd.)

36, Chandan Nagar, Jalandhar City. Tel.: 0181-2621630

# $\sim$ Syllabus $\sim$

LTP

#### 3 - -

#### 1. FUNCTIONAL BLOCKS OF A COMPUTER

CPU, memory, input-output subsystems, control unit. Instruction set architecture of a CPU-registers, instruction execution cycle, RTL interpretation of instructions, addressing modes, instruction set. Case study - instruction set of 8085 processor.

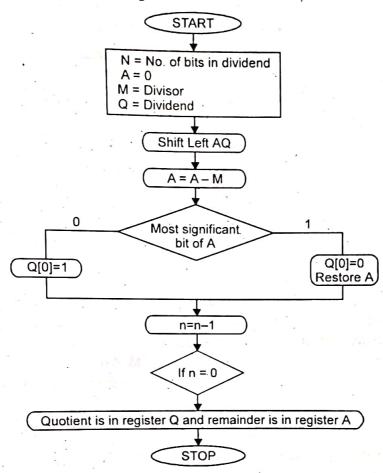

Data representation: Signed number representation, fixed and floating point representations, character representation. Computer arithmetic - integer addition and subtraction, ripple carry adder, carry look-ahead adder, etc. multiplication - shift and add, Booth multiplier, carry save multiplier, etc. Division restoring and non-restoring techniques, floating point arithmetic.

#### 2. INTRODUCTION TO X86 ARCHITECTURE

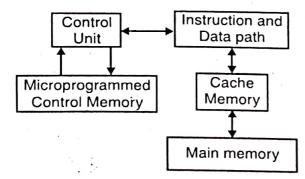

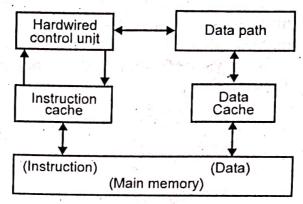

CPU Control Unit Design: Hardwired and micro-programmed design approaches, Case study - design of a simple hypothetical CPU.

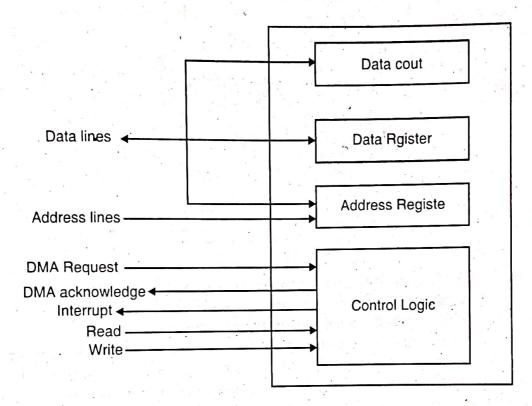

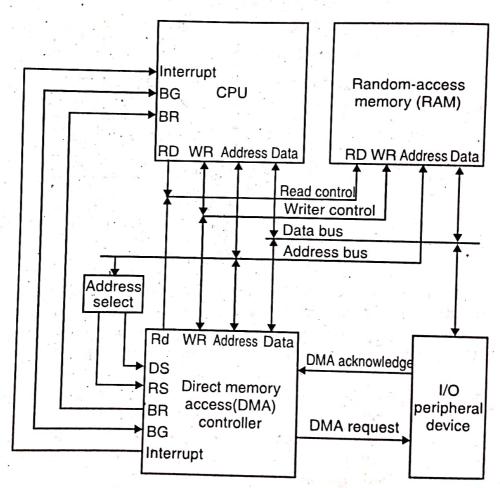

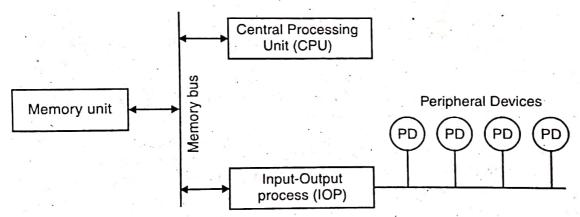

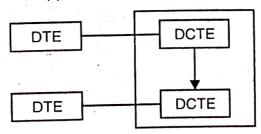

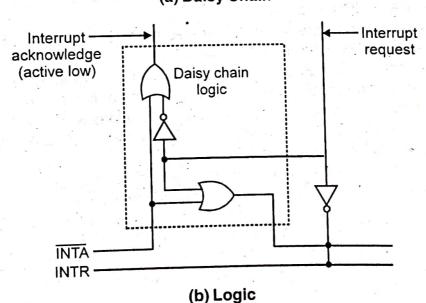

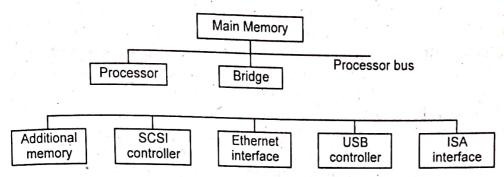

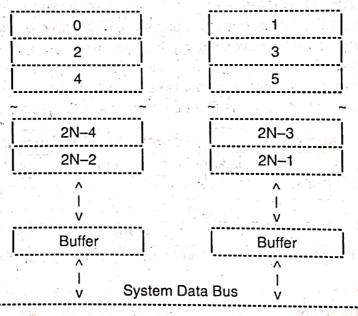

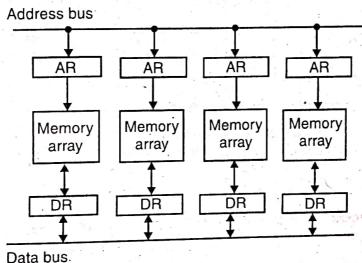

Memory system design: Semiconductor memory technologies, memory organization. Peripheral devices and their characteristics: Input-output subsystems, I/O device interface, I/O transfers - program controlled, interrupt driven and DMA, privileged and non-privileged instructions, software interrupts and exceptions. Programs and processes - role of interrupts in process state transitions, I/O device interfaces - SCII, USB.

#### 3. PIPELINING

Basic concept of pipelining, throughput and speedup, pipeline hazards.

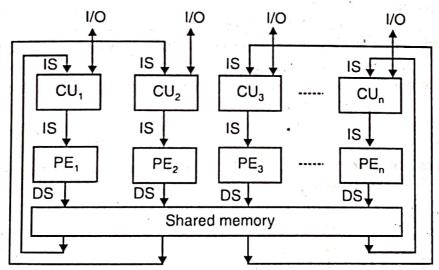

Parallel Processors: Introduction to parallel processors, Concurrent access to memory and cache coherency.

#### 4. MEMORY ORGANISATION

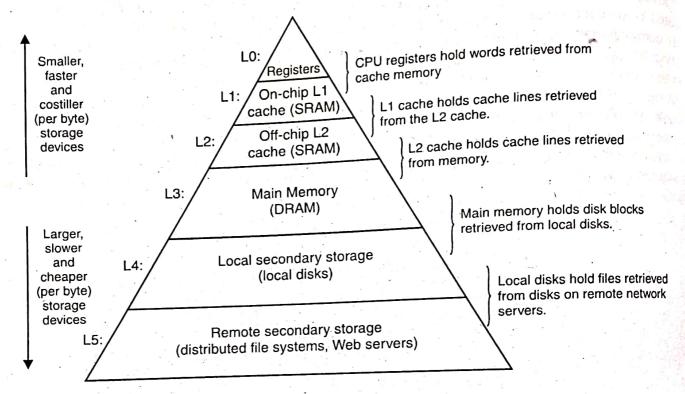

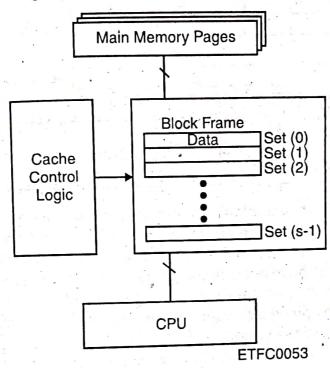

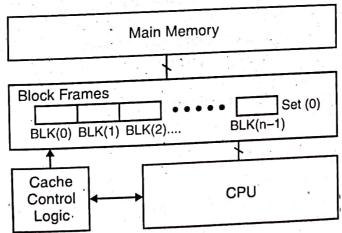

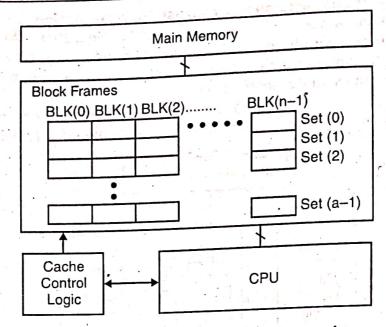

Memory interleaving, concept of hierarchy memory organization, cache memory, cache size vs. block size, mapping functions, replacement algorithms, write policies.

# $\sim$ Contents $\sim$

|    | Punjab Technical University Question Tupe: (Dec. 2019) |      | 5.      |

|----|--------------------------------------------------------|------|---------|

| 1. | Functional Blocks of a Computer                        |      | 9-7     |

| 2. | Introduction to x86 Architecture                       |      | 72-13;  |

| 3. | Pipelining                                             | 1210 | 133-165 |

| 4. | Memory Organisation                                    |      | 166-190 |

|    | Model Test Papers                                      |      | 191-192 |

# PUNJAB TECHNICAL UNIVERSITY QUESTION PAPERS

## UNIVERSITY QUESTION PAPER, DEC.-2019

#### **SECTION - A**

Q 1. What is the difference between machine and instruction cycles?

Ans. Refer to Chapter No. 1 Q.No. 49

Q 2. What are the memory reference instructions? Give examples.

Ans. Refer to Chapter No. 1 Q.No. 12

Q 3. What is hardwired control? What are its advantages?

Ans. Refer to Chapter No. 2 Q.No. 117

Q 4. What is control memory?

Ans. Refer to Chapter No. 2 Q.No. 31

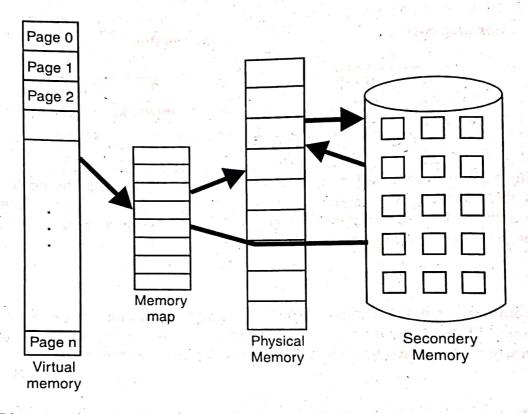

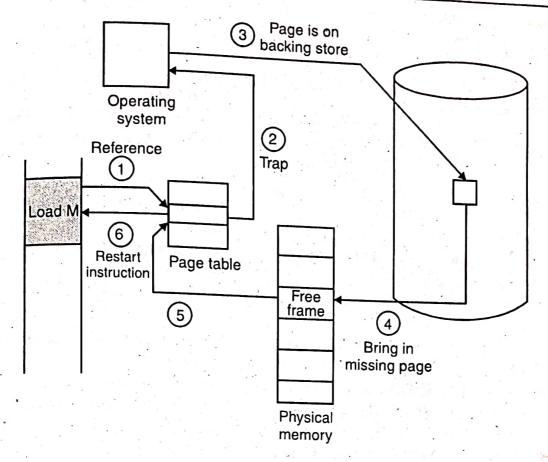

Q 5. Explain the concept of virtual memory.

Ans. Refer to Chapter No. 4 Q.No. 28

Q 6. What is the role of ROM memory in a computer system?

Ans. Refer to Chapter No. 4 Q.No. 57

Q 7. What is register transfer language?

Ans. Refer to Chapter No. 1 Q.No. 1

Q 8. What is an instruction pipeline?

Ans. Refer to Chapter No. 3 Q.No. 3

Q 9. What are registers? Can they be called memory?

Ans. Refer to Chapter No. 4 Q.No. 58

Q 10. What is Microprocessor?

Ans. Refer to Chapter No. 2 Q.No. 118

#### **SECTION – B**

Q 11. What is memory management hardware? Explain.

Ans. Refer to Chapter No. 4 Q.No. 22

Q 12. Explain the organization of a typical computer system.

Ans. Refer to Chapter No. 1 Q.No. 11

Q 13. What is pipelined control ? Explain.

Ans. Refer to Chapter No. 3 Q.No. 5

Q 14. What are multilevel memory systems? Explain with the help of a diagram.

Ans. Refer to Chapter No. 4 Q.No.: 27

Q 15. How does a RISC organize CPU works? What are its characteristics and advantages?

Ans. Refer to Chapter No. 1 Q.No. 51, 52 & 53

COA

# Chapter

1

# Functional Blocks of a Computer

#### **Contents**

CPU, memory, input-output subsystems, control unit. Instruction set architecture of a CPU-registers, instruction execution cycle, RTL interpretation of instructions, addressing modes, instruction set. Case study - instruction set of 8085 processor.

**Data representation**: Signed number representation, fixed and floating point representations, character representation. Computer arithmetic - integer addition and subtraction, ripple carry adder, carry look-ahead adder, etc. multiplication - shift and add, Booth multiplier, carry save multiplier, etc. Division restoring and non-restoring techniques, floating point arithmetic.

### POINTS TO REMEMBER

- A register transfer language is a system for expressing in symbolic form the micro operation sequences among the registers of digital module.

- The symbolic notation used to describe the micro-operation transfer among registers is known as register transfer language.

- Microoperation is an elementary operation performed with the data stored in registers.

- Register transfer microoperations transfer binary information from one register to another.

- Arithmetic microoperations perform arithmetic operations on numeric data stored in registers.

- Logic microoperations perform bit manipulation operations on non-numeric data stored in registers.

- Shift microoperations perform shift operations on data stored in registers.

- Register transfer language can also be used to facilitate the design process of digital systems.

- Computer registers are designated by capital letters to denote the function of the register.

- Control condition is terminated with a colon.

- Register transfer microoperation does not change the information content when the binary information moves from the source register to the destination register.

- The basic arithmetic micro operations are addition, subtraction, increment, decrement, and shift.

- Arithmetic shifts are explained later in conjunction with the shift microoperations.

- These microoperations are implemented with a combinational circuit or with a binary upward counter.

- The increment and decrement microoperations are symbolized by plus-one and minus-one operations, respectively.

- The arithmetic microoperations can be implemented in one composite arithmetic circuit.

- The hardware implementation of logic microoperations requires that logic gates be inserted for each bit or pair of bits in the registers to perform the required logic function.

- The digital circuit that forms the arithmetic sum of two bits and a previous carry is called a full-adder.

- The digital circuit that generates the arithmetic sum of two binary numbers of any lengths is B

- called a pinary adder.

Shift register is a register that is capable of shifting its binary information in one or both directions. Shift register is a register trial is capable of sequence of microoperations it.

The internal organization of a digital system is defined by the sequence of microoperations it. B

- The internal organization of a digital system. The general purpose digital computer is capable of performs on data stored in its registers. The general purpose digital computer is capable of B executing various micro-operations.

- An instruction code is a binary code that specifies a sequence of micro operations for the computer. Instruction code together with data stored in memory. B

- The operation code of an instruction is a group of bits that define operations such as add, B subtract, multiply, shift, complement etc.

- Computer instructions are normally stored in consecutive memory locations and are executed sequentially one at a time. The control reads an instruction from a specific address in a memory B

- The program counter (P.C) has 12 bits and it holds address of the next instruction to be needed from memory after the current instruction is executed.

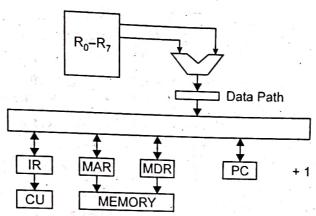

- A basic computer has eight registers, a memory unit and a control unit. Paths must be provided to transfer information from one register to another and between memory and registers.

- A computer has three instruction code format. These are:

- (i) Memory Instruction format

- (ii) Register Instruction format

- (iii) I/O Instruction format.

- There are two types of control organisation in a computer, that are, hardware control and B microprogrammed control.

- In a hardwired organisation, the control logics are implemented with gates, flip-flops, decoders and other digital circuits.

- In a microprogrammed control, any required changes or modification can be done by operating B the microprocessor in the control memory.

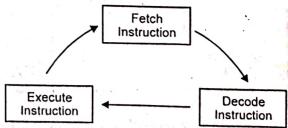

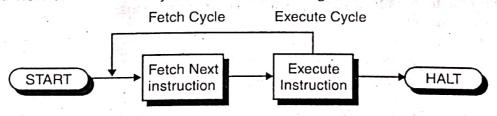

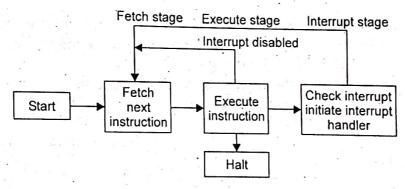

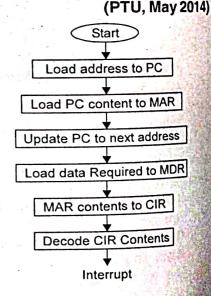

- The program is executed in a computer by goining through a cycle for each instruction. Each B instruction cycle is subdivided into a sequence of subcycles or phases.

- In a basic computer each instruction cycle consists of the following phases: B.

- (i) Fetch an instruction from the memory.

- (ii) Decode the instruction.

- (iii) Read the effective address from memory if the instruction has an indirect address.

- (iv) Execute the instruction.

- A pseudo instruction is not a machine instruction but rather an instruction to the assembler B giving information about some phases of the translation.

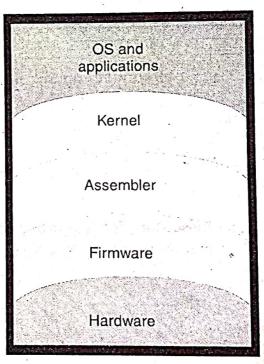

- The translation of the symbolic program into binary is done by a special program called an assembler.

- A system program that translate a program written in a high level programming language to a machine language is called a compiler.

- Subroutine is a set of common instructions that can be used in a program many times. Each B. time a subroutine is used in the main part of program, a brach is executed to the beginning of the subroutine. After the subroutine is executed, a brench is made back to the main program.

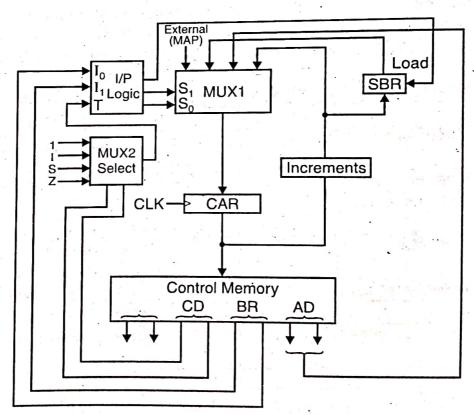

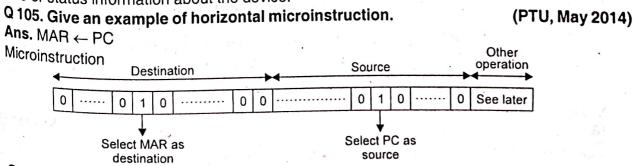

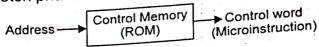

- A control unit whose binary control variables are stored in memory is called a microprogrammed control unit. Each word in control memory contrains within it a micro instruction.

- The micro instruction specifies one or more operations for the system. A sequence of micro instruction specifies constitutes a micro program.

- Mapping is a process of transformation the instruction code bits to an address in control memory where the routine is located.

- Most computer instructors can be classified into three categories :

- (i) Data transfer instructions

- (ii) Data manipulation instructions

- (iii) Program control instructions.

- A computer with large number of instructions is known as 'complex instruction set computer', abbreviated as CISC.

- A computer which uses fewer instructions with simple constructs, so they can be classified much faster within CPU are known as 'Reduced Instruction Intructor Set Computers', abbrivated as RISC.

#### **QUESTION-ANSWERS**

Q 1. What is register transfer language? Explain it with example.

(PTU, Dec. 2019; May 2018)

Ans. Register Transfer Language: The symbolic notation used to describe the micro-operation transfer among registers is known as register transfer language. A register transfer language is a systme for expressing in symbolic form the microoperation sequences among the registers of digital module. A kind of hardware description language (HDL) used in describing the registers of a computer or digital electronic system, and the way in which data is transferred between them.

Register transfer language is:

- A symbolic language

- A convenient tool for describing the internal organization of digital computers

- Can also be used to facilitate design process of digital systems.

**Example of Register Transfer Language :** Suppose let us take an example of information transfer from one register to another by means of replacement operator.

R2 < R1

Which denotes transfer of content of register R1 into register R2.

Q 2. Explain the concept of register transfer?

$\Omega$ r

Explain the block diagram of register with its timing diagram.

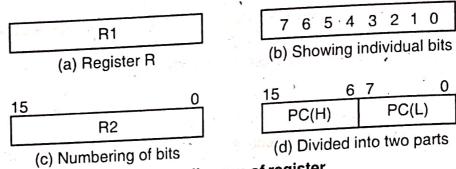

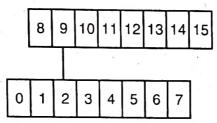

Ans. Computer registers are designated by capital letters (sometimes followed by numerals) to denote the function of the register. For example, the register that holds an address for the memory unit is usually called a memory address register and is designated by the name MAR. Other designations for registers are PC (for program counter), IR (for instruction register), and  $R_1$  (for processor register). The individual flip-flops in an n-bit register are numbers in sequence from 0 through n-1, starting from 0 in the rightmost position and increasing the numbers toward the left. Fig. shows the representation of registers in block diagram form. The most common way to represent a register is by a rectangular box with the name of the register inside, as in Fig.(a). The individual bits can be distinguished as in (b). The numbering of bits in a 16-bit register can be marked on top of the box as shown in (c). A 16-bit register is partitioned into two parts in (d). Bits 0 through 7 are assigned the symbol L (for low byte) and bits 8 through 15 are assigned the symbol H (for high byte). The name of the 16-bit register is PC.

The symbol PC (0-7) or PC (L) refers to the low-order byte and PC (8-15) or PC (H) to the high-order byte.

Block diagram of register

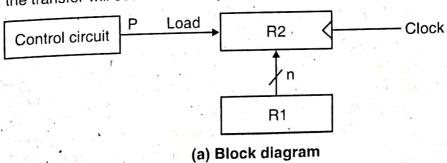

Information transfer from one register to another is designated in symbolic form by means of a replacement operator. The statement R2  $\rightarrow$  R1 denotes a transfer of the content of register R<sub>1</sub> into register  $R_2$ . It designates a replacement of the content of  $R_2$  by the content of  $R_1$ . By definition, the content of the source register  $R_1$  does not change after the transfer.

A statement that specifies a register transfer implies that circuits are available from the output of the source register to the inputs of the destination register and that the desigation register has a parallel load capability. Normally, we want the transfer to occur only under a predetermined control condition. This can be shown by means of an if-then statement.

If

$$(P = 1)$$

then  $(R2 \leftarrow R1)$

where P is a control signal generated in the control section. It is sometimes convenient to separate the control variables from the register transfer operation by specifying a control function. A control function is a Boolean variable that is equal to 1 or 0. The control function is included in the statement as follows:

The control condition is terminated with a colon. It symbolizes the requirement that the transfer operation be executed by the hardware only if P = 1.

Every statement written in a register transfer notation implies a hardware construction for implementing the transfer. The above fig. shows the block diagram that depicts the transfer from R<sub>1</sub> to  $R_2$ . The n outputs of register  $R_1$  are connected to the n inputs of register  $R_2$ . The letter n will be used to indicate any number of bits for the register. It will be replaced by an actual number when the length of the register is known. Register  $R_2$  has a load input that is activated by the control variable P. It is assumed that the control variable is synchronized with the same clock as the one applied to the register. As shown in the timing diagram (b), P is activated in the control section by the rising edge of a clock pulse at time t. The next positive transition of the clock at time t + 1 finds the load input active and the data inptus of  $R_2$  are then loaded into the register in parallel. P may go back to 0 at time t+1; otherwise, the transfer will occur with every clock pulse transition while P remains active.

#### (b) Timing diagram

#### **Timing diagram**

The basic symbols of the register transfer notations are listed in table. Registers are denoted by capital letters, and numerals may follow the letters. Parentheses are used to denote a part of a register by specifying the range of bits or by giving a symbol name to a portion of a register. The arrow denotes a transfer of information and the direction of transfer. A comma is used to separate two or more operations that are executed at the same time. The statement

$$T: R2 \leftarrow R1, R1 \leftarrow R2$$

denotes an operation that exchanges the contents of two registers during one common clock pulse provided that T=1. This simultaneous operation is possible with registers that have edge-triggered flip-flops.

| Symbol                 | Description                     | Example            |

|------------------------|---------------------------------|--------------------|

| Letters (and numerals) | Denotes a register              | MAR, R2            |

| Parentheses ()         | Denotes a part of a register    | R2 (0 – 7), R2 (L) |

| Arrow ←                | Denotes transfer of information | R2 ← R1            |

| Comma ,                | Separates two microoperations   | R2 ← R1, R1 ← R2   |

Table: Basic Symbols for Register Transfers

#### Q 3. Explain the various microoperations performed in registers.

Ans. A microoperation is an elementary operation performed with the data stored in registers. The microoperations most often encountered in digital computers are classified into four categories:

- 1. Register transfer microoperations transfer binary information from one register to another.

- 2. Arithmetic microoperations perform arithmetic operations on numeric data stored in registers.

- 3. Logic microoperations perform bits manipulation operations on non-numeric data stored in registers.

## 4. Shift microoperations perform shift operations on data stored in registers.

The register transfer microoperation does not change the information content when the binary information moves from the source register to the destination register. The other three types of microoperations change the information content during the transfer.

#### Q 4. Explain arithmetic microoperations.

Ans. The basic arithmetic micro operations are addition, subtraction, increment, decrement, and shift. Arithmetic shifts are explained later in conjunction with the shift microoperations. The arithmetic microoperation defined by the statement.

$R_3 \leftarrow R_1 + R_2$  specifies an add microoperation. It states that the contents of register  $R_1$  are added to the contents of register R2 and the sum transferred to register R3. To implement this statement with hardware we need three registers and the digital component that performs the addition

operation. The other basic arithmetic microoperations are listed in Table. Subtraction is most often implemented through complementation and addition. Instead of using the minus operator, we can specify the subtraction by the following statement:

$$R3 \leftarrow R1 + \overline{R2} + 1$$

$\overline{R2}$  is the symbol for the 1's complement of R2. Adding 1 to the 1's complement produces the 2's complement. Adding the contents of R1 to the 2's complement of R2 is equivalent to R1 – R2.

| Symbolic Designation | Description                                    |

|----------------------|------------------------------------------------|

| R3 ← R1 + R2         | Contents of R1 plus R2 transferred to R3       |

| R3 ← R1 – R2         | Conents of R1 minus R2 transferred to R3       |

| R2 ← R2              | Complement the contents of R2 (1's complement) |

| R2 ← R2 + 1          | 2's complement the contents of R2 (            |

| R3 ← R1 + R2 + 1     | R1 plus the 2's complement of R2 (subtraction) |

| R1 ← R1 + 1          | Increment the contents of R1 by one            |

| R1 ← R1 – 1          | Decrement the contents of R1 by one            |

**Table: Arithmetic Microoperations**

The increment and decrement microoperations are symbolized by plus-one and minus-one operations, respectively. These microoperations are implemented with a combinational circuit or with a binary up-down counter.

The arithmetic operations of multiply and divide are not listed in table. These two operations are valid arithmetic operations but are not included in the basic set of microoperations. The only place where these operations can be considered as microoperations is in a digital system, where they are implemented by means of a combinational circuit. In such a case, the signals that perform these operations propagate through gates, and the result of the operation can be transferred into a destination register by a clock pulse as soon as the output signal propagates through the combinational circuit. In most computers, the multiplication operation is implemented with the sequence of add and shift microoperations. Division is implemented with a sequence of subtract and shift microoperations. To specify the hardware in such a case requires a list of statements that use the basic microoperations of add, subtract and shift.

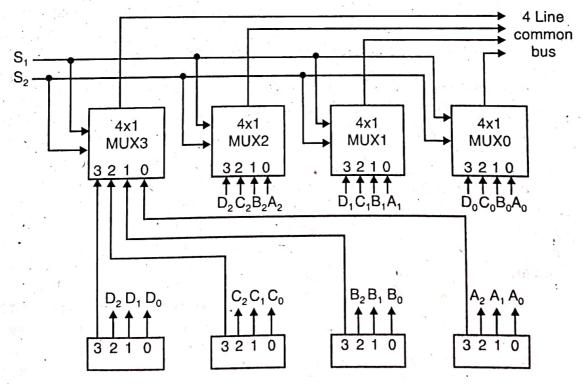

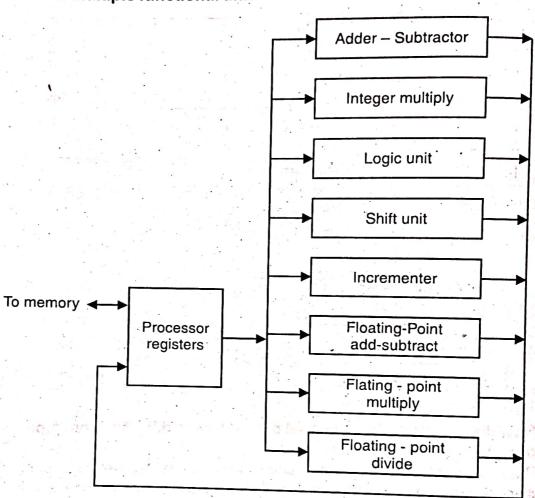

# Q 5. Implement the arithmetic circuit using arithmetic microoperations.(PTU, May 2017)

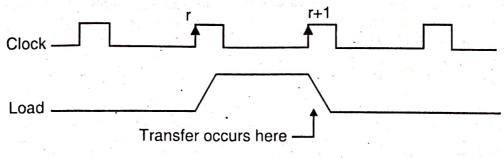

Ans. The arithmetic microoperations can be implemented in one composite arithmetic circuit. The basic component of an arithmetic circuit is the parallel adder. By controlling the data inputs to the adder, it is possible to obtain different types of arithmetic operations.

The diagram of a 4-bit arithmetic circuit is shown in fig. It has four full-adder circuits that constitute the 4-bit adder and four multiplexers for choosing different operations. There are two 4-bit inputs A and B and a 4-bit output D. The four inputs from A go directly to the X inputs of the binary adder. Each of the four inputs from B is connected to the data inputs of the multiplexers. The multiplexers data inputs also receive the complement of B. The other two data inputs are connected to logic-0 and logic-1. Logic-0 is a fixed voltage value (0 volts for TTL integrated circuits) and the logic-1 signal can be generated through an inverter whose input is 0. The four multiplexers are controlled by two selection inputs  $S_1$  and  $S_0$ . The input carry  $C_{\rm in}$  goes to the carry input of the FA in the least significant position. The other carries are connected from one stage to the next.

The output of the binary adder is calculated from the following arithmetic sum:

$$D = A + Y + C_{in}$$

where A is the 4-bit binary number at the X inputs and Y is the 4-bit binary number at the Y inputs of the binary adder. Cin is the input carry, which can be equal to 0 or 1. Note that the symbol + in the equation above denotes an arithmetic plus. By controlling the value of Y with the two selection inputs  $S_1$  and  $S_0$  and making  $C_{in}$  equal to 0 or 1, it is possible to generate the eight arithmetic microoperations listed in table.

| Select                     |                                               |                                | 1 Custout                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                        | Microoperation |  |  |

|----------------------------|-----------------------------------------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--|--|

| S <sub>0</sub>             | C <sub>in</sub>                               | Υ                              | $D = A + Y + C_{in}$                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                        |                |  |  |

| 0<br>0<br>1<br>1<br>0<br>0 | 0<br>1<br>0<br>1<br>0<br>1                    | B<br>B<br>B<br>B<br>0<br>0     | D = A + B $D = A + B - 1$ $D = A + B$ $D = A + B + 1$ $D = A$ $D = A + 1$ $D = A + 1$                                                                                                    | Add Add with carry Subtract with borrow Subtract Transfer A Increment A Decrement A Transfer A                                                                                                                                                                                                                                                                                                         |                |  |  |

| •                          | Select  S <sub>0</sub> 0  0  1  0  1  1  0  1 | S <sub>0</sub> C <sub>in</sub> | So         Cin         Y           0         0         B           0         1         B           1         0         B           1         1         B           1         1         B | Select         Y         D = A + Y + C <sub>in</sub> 0         0         B         D = A + B           0         1         B         D = A + B - 1           1         0         B         D = A + B - 1           1         1         B         D = A + B           1         1         B         D = A + B + 1           0         0         D = A           0         1         0         D = A + 1 |                |  |  |

**Table: Arithmetic Circuit Function Table**

When  $S_1 S_0 = 00$ , the value of B is applied to the Y inputs of the adder. If  $C_{in} = 0$ , the output D = A + B. If  $C_{in}$  = 1, output D = A + B + 1. Both cases perform the add microperation with or without adding the input carry.

When  $S_1 S_0 = 01$ , the complement of B is applied to the Y inputs of the adder. If  $C_{in} = 1$ , then  $D = A + \overline{B} + 1$ . This produces A plus the 2's complement of B, which is equivalent to a subtraction of A - B. When  $C_{in} = 0$ , then D = A +  $\overline{B}$  + 1. This produces A plus the 2's complement of B, which is equivalent to a subtraction of A – B. When  $C_{in} = 0$ , then D = A +  $\overline{B}$ . This is equivalent to a subtract with borrow, that is, A - B - 1.

When  $S_1 S_0 = 10$ , the inputs from B are neglected, and instead, all 0's are inserted into the y inputs. The output becomes  $D = A + 0 + C_{in}$ . This gives D = A when  $C_{in} = 0$  and D = A + 1 when  $C_{in} = 0$ = 1. In the first case we have a direct transfer from input A to output D. In the second case, the value of A is increment by 1.

When  $S_1 S_0 = 11$ , all 1's are inserted into the Y inputs of the adder to produce the decrement operation D = A - 1 when  $C_{in} = 0$ . This is because a number with all 1's is equal to the 2's complement of 1 (the 2's complement of binary 0001 is 1111). Adding a number A to the 2's complement of 1 produces F = A + 2's complement of 1 = A - 1. When  $C_{in} = 1$ , then D = A - 1 + 1 = A, which causes a direct transfer from input A to output D. Note that the microoperation D = A is generated twice, so there are only seven distinct microoperations in the arithmetic circuit.

#### Q 6. What are logic microoperations?

Ans. Logic microperations: Logic microoperations specify binary operations for strings of bits stored in registers. These operations consider each bit of the register separately and treat them as binary variables. For example, the exclusive-OR microoperation with the contents of two registers R1 and R2 is symbolized by the statement.

It specifies a logic microoperation to be executed on the individual bits of the registers provided that the control variable P = 1. As a numerical example, assume that each register has four bits. Let the content of R1 be 1010 and the content of R2 be 1100. The exclusive-OR microopertion stated above symbolizes the following logic computation:

1010 Content of R1

1100 Content of R2

#### 0110 Content of R1 after P = 1

The content of R1, after the execution of the microoperation, is equal to the bity-by-bit exclusive-OR operation on pairs of bits in R2 and previous values of R1. The logic microoperations are seldom used in scientific computations, but they are very useful for bit manipulation of binary data and for

Special symbols will be adopted for the logic microoperations OR, AND and complement, to distinguish them from the corresponding symbols used to express Boolean functions. The symbol V will be used to denote an OR microoperation and the symbol to denote an AND microoperation. The complement microoperation is the same as the 1's complement and uses a bar on top of the symbol that denotes the register name. By using different symbols, it will be possible to differentiate between a logic microoperation and a control (or Boolean) function. Another reason for adopting two sets of symbols is to able to distinguish the symbol +, when used to symbolize an arithmetic plus, from a logic OR operation. Although the + symbol has two meanings, it will be possible to distinguish between them by noting where the symbol occurs. When the symbol + occurs in a microoperation, it will denote

an OR operation. We will never use it to symbolize an OR microoperation. For example, in the statement  $P+Q:R1 \leftarrow R2+R3, R4 \leftarrow R5 \ VR6$

the + between P and Q is an OR operation between two binary variables of a control function. The + between R2 and R3 specifies an add microoperation. The OR microoperation is designated by the symbol V between registers R5 and R6.

# Q 7. Explain Hardware implementation of logic microoperation.

Ans. Hardware Implementation: The hardware implementation of logic microoperations requires that logic gates be inserted for each bit or pair of bits in the registers to perform the required logic function. Although there are 16 logic microoperations, most computers use only four – AND, OR, XOR (exclusive-OR), and complement-from which all others can be derived.

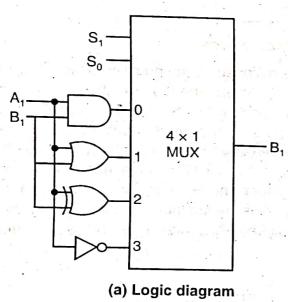

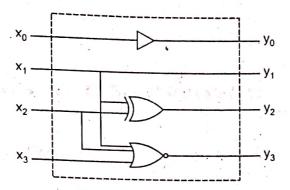

Fig. shows one stage of a circuit that generates the four basic logic microoperations. It consists of four gates and a multiplexer. Each of the four logic operations is generated through a gate that performs the required logic. The outputs of the gates are applied to the data inputs of the multiplexer. The two selection inputs  $S_1$  and  $S_0$  choose one of the data inputs of the multiplexer and direct its value to the output. The diagram shows one typical stage with subscript i. For a logic circuit with n bits, the diagram must be repeated n times for I = 0, 1, 2, ...., n - 1. The selection variables are applied to all stages. The function table in fig. (b) lists the logic microoperations obtained for each combination of the selection variables.

| S  | Sı  | Output             | Operation  |

|----|-----|--------------------|------------|

| 0  | 0   | $E = A \cap B$     |            |

| 0  | 1.  | E = AUB            | OR         |

| 1. | 0 ; | E = A⊕B            | XOR        |

| 94 | 1.  | $E = \overline{A}$ | Complement |

(b) Function circuits

#### One stage of logic circuit

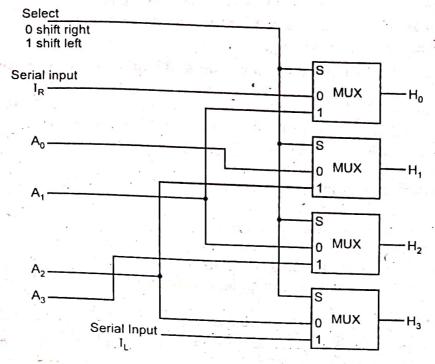

Q 8. What are shift microoperations? Explain with example. Design 4 bit combinational circuit for shifter.

(PTU, May 2018, 2015)

Ans. Shift Microoperations: Shift microoperations are used for serial transfer of data. They are also used in conjunction with arithmetic, logic and other data-processing operations. The contents of a register can be shifted to the left or the right. At the same time that the bits are shifted, the first flip-flop receives its binary information from the serial input. During a shift-left operation the serial input transfers a bit into the rightmost position. During a shift-right operation the serial input transfers a bit into the leftmost position. The information transferred through the serial input determines the type of shift. There are three types of shifts: logical, circular, and arithmetic.

A logical shift is one that transfers 0 through the serial input. We will adopt the symbols shl and shr for logical shift-left and shift-right microoperations. For example:

$$R1 \leftarrow shl R1$$

$R2 \leftarrow shr R2$

are two microoperations that specify a 1-bit shift to the left of the content of register R1 and a 1. bit shift to the right of the content of register R2. The register symbol must be the same on both sides of the arrow. The bit transferred to the end position through the serial input is assumed to be 0 during a logical shift.

The circular shift (also known as a rotate operation) circulates the bits of the register around the two ends without loss of information. This is accomplished by connecting the serial outpt of the shift register to its serial input. We will use the symbols cill and cir for the circular shift left and right, respectively. The symbolic notation for the shift microoperations is shown in table.

| Symbolic designation                                                                                                                                                            | Description           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| $R \leftarrow \text{shl } R$ $R \leftarrow \text{shr } R$ $R \leftarrow \text{cil } R$ $R \leftarrow \text{cir } R$ $R \leftarrow \text{ashr } R$ $R \leftarrow \text{ashr } R$ | Shift-left register B |

#### **Table: Shift Microoperations**

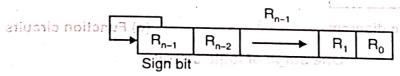

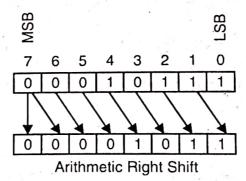

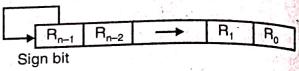

An arithmetic shift is a microoperation that shifts a signed binary number to the left or right, An arithmetic shift-left multiplies a signed binary number by 2. An arithmetic shift-right divides the number by 2. Arithmetic shifts must leave the sign bit unchanged because the sign of the number remains the same when it is multiplied or divided by 2. The leftmost bit in a register holds the sign bit, and the remaining bits hold the number. The sign bit is 0 for positive and 1 for negative. Negative numbers are in 2's complement form. Fig. shows a typical register of n bits. Bit  $R_{n-1}$  in the leftmost position holds the sign bit.  $R_{n-2}$  is the most significant bit of the number and  $R_0$  is the least significant bit. The arithmetic shift-right leaves the sign bit unchanged and shifts the number (including the sign bit) to the right. Thus  $R_{n-1}$  remains the same,  $R_{n-2}$  receives the bit from  $R_{n-1}$ , and so on for the other bits in the register. The bit in R0 is lost.

## O a. What are shift microoper their think oitematin's example. Design 4 bit combinational

The arithmetic shift-left inserts a 0 into R<sub>0</sub>, and shifts all other bits to the left. The initial bit of  $R_{n-1}$  is lost and replaced by the bit from  $R_{n-2}$ . A sign reversal occurs if the bit in  $R_{n-1}$  changes in value after the shift. This happen if the multiplication by 2 causes an overflow. An overflow occurs after an arithmetic shift left if initially, before the shift,  $R_{n-1}$  is not equal to  $R_{n-2}$ . An overflow flip-flop Vs can be used to detect an arithmetic shift-left overflow.

$$Vs = R_{n-1} \oplus R_{n-2}$$

equivalent individual series and Contarago in the series of the series shift. V<sub>s</sub> must be transferred into the overflow flip-flop with the same clock pulse that shifts the register. shelp logical state of and staffight more operations. For example:

#### 4-bit combinational circuit shifter

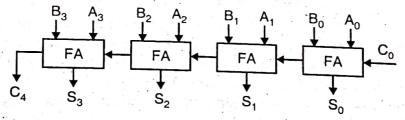

# Q 9. To implement add microoperation with hardware.

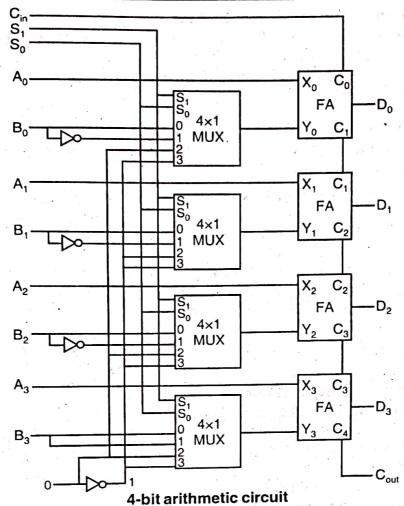

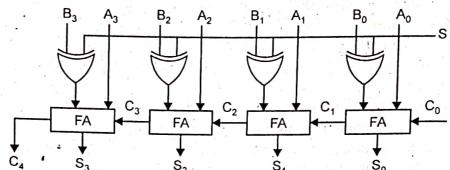

Ans. Binary Adder: To implement the add microoperation with hardware, we need the registers that hold the data and the digital component that performs the arithmetic addition. The digital circuit that forms the arithmetic sum of two bits and a previous carry is called a full-adder. The digital circuit that generates the arithmetic sum of two binary numbers of any lengths is called a binary adder. The binary adder is constructed with full-adder circuits connected in cascade, with the output carry from one full-adder connected to the input carry of the next full-adder. Fig. shows the interconnections of four full-adders (FA) to provide a 4-bit binary adder. The augend bits of A and the addend bits of B are designated by subscript numbers from right to left, with subscript 0 denoting the low-order bit. The carries are connected in a chain through the full-adders. The input carry to the binary adder is  $C_0$  and the output carry is  $C_4$ . The S outputs of the full-adders generate the required sum bits.

4-bit binary adder

An n-bit binary adder requires n full-adders. The output carry from each full-adder is connected to the input carry of the next-high-order full-adder. The n data bits for the A inputs come from one register (such as R1), and the n data bits for the B inputs come from another register (such as R2). The sum can be transferred to a third register or to one of the source registers (R1 or R2), replacing its previous content.

Q 10. Differentiate between register and memory. (PTU, Dec. 2011)

Ans. Registers are the memory space provided by the processor for storing temporary values

on which the operation is currently performing. And the memory locations are usually refered to as physical memory addresses i.e. RAM addresses. The data are brought to and from the registers are from the physical memory. All data and instructions are stored in the physical memory and the data are brought to the registers for execution.

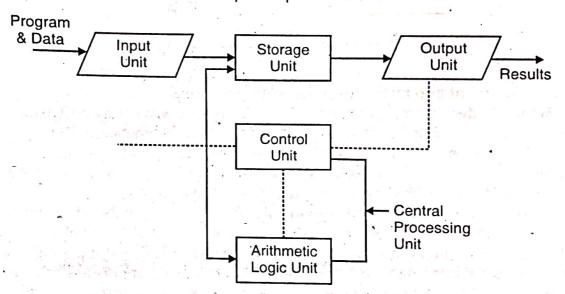

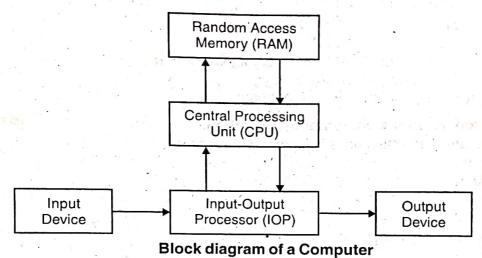

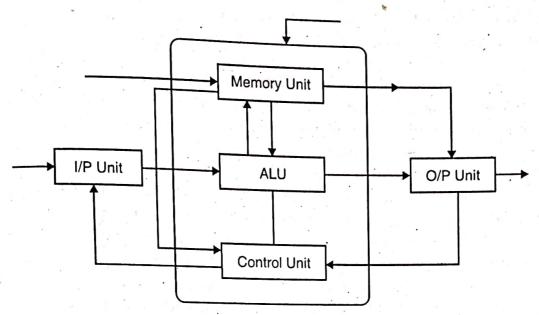

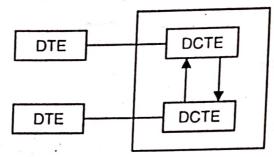

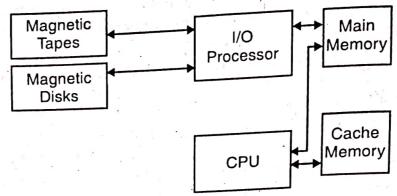

Q 11. Draw the block diagram of computer and explain its various components.

(PTU, Dec. 2019)

Ans. Block Diagram of Computer: A computer can process data, pictures, sound and graphics. They can solve highly complicated problems quickly and accurately. A computer as shown in fig. performs basically five major computer operations or functions irrespective of their size and make. These are

- 1. It accepts data or instructions by way of input

- 2. It stores data

- 3. It can process data as required by the user

- 4. It gives results in the form of output, and

- 5. It controls all operations inside a computer.

We discuss below each of these computer operations:

#### **Basic Computer Operations**

- 1. Input: This is the process of entering data and programs into the computer system. You should know that computer is an electronic machine like any other machine which takes as inputs raw data and performs some processing giving out processed data. Therefore, the input unit takes data from us to the computer in an organized manner for processing.

- 2. Storage: The process of saving data and instructions permanently is known as storage. Data has to be fed into the system before the actual processing starts. It is because the processing speed of Central Processing Unit (CPU) is so fast that the data has to be provided to CPU with the same speed. Therefore the data is first stored in the storage unit for faster access and processing. This storage unit or the primary storage of the computer system is designed to do the above functionality. It provides space for storing data and instructions.

The storage unit performs the following major functions:

- All data and instructions are stored here before and after processing.

- Intermediate results of processing are also stored here.

- 3. Processing: The task of performing operations like arithmetic and logical operations is

called processing. The Central Processing Unit (CPU) takes data and instructions from the storage unit and makes all sorts of calculations based on the instructions given and the type of data provided. It is then sent back to the storage unit.

- 4. Output: This is the process of producing results from the data for getting useful information. Similarly, the output produced by the computer after processing must also be kept somewhere inside the computer before being given to you in human readable form. Again the output is also stored inside the computer for further processing.

- 5. Control: The manner how instructions are executed and the above operations are performed. Controlling of all operations like input, processing and output are performed by control unit. It takes care of step by step processing of all operations inside the computer.

Functional Units: In order to carry out the operations mentioned in the previous section the computer allocates the task between its various functional units. The computer system is divided into three separate units for its operation. They are:

- 1. Arithmetic logical unit

- 2. Control unit

- 3. Central processing unit.

- 1. Arithmetic Logical Unit (ALU):

Logical Unit: After you enter data through the input device it is stored in the primary storage unit. The actual processing of the data and instruction are performed by Arithmetic Logical Unit. The major operations performed by the ALU are addition, subtraction, multiplication, division, logic and compression. Data is transferred to ALU from storage unit when required. After processing the output is returned back to storage unit for further processing or getting stored.

- 2. Control Unit (CU): The next component of computer is the Control Unit, which acts like the supervisor seeing that things are done in proper fashion. Control unit is responsible for co-ordinating various operations using time signal. The control unit determines the sequence in which computer programs and instructions are executed. Things like processing of programs stored in the main memory, interpretation of the instructions and issuing of signals for other units of the computer to execute them. It also acts as a switch board operator when several users access the computer simultaneously. Thereby it coordinates the activities of computer's peripheral equipment as they perform the input and output.

- 3. Central Processing Unit (CPU): The ALU and the CPU of a computer system are jointly known as the central processing unit. You may call CPU as the brain of any computer system. It is just like brain that takes all major decisions, makes all sorts of calculations and directs different parts of the computer functions by activating and controlling the operations.

- Q 12. What are the memory reference instructions? Give examples. (PTU, Dec. 2019)

Ans. These instructions refer to memory address as an operand. The other operand is always accumulator. Specifies 12-bit address 3-bit opcode and 1-bit addressing mode for direct and indirect addressing.

| 15 | 14      | 12     | 2 11          | _0 |

|----|---------|--------|---------------|----|

| 1  | 1184 2- | Opcode | Memory Addres | s  |

**Example:** IR register contains = 000/xxxxxxxxxxxx, i.e. ADD after fetching and decoding of instruction we find out that it is a memory reference instruction for ADD operation.

Hence,

$$DR \leftarrow M[AR]$$

$AC \leftarrow AC + DR, SC \leftarrow 0$

Q 13. What do you understand by floating point arithmetic?

(PTU, Dec. 2011)

Ans. Floating-point arithmetic is considered an esoteric subject by many people. This is rather surprising because floating-point is ubiquitous in computer systems. Almost every language has a floating-point data type; computers from PCs to supercomputers have floating-point accelerators; most compilers will be called upon to compile floating-point algorithms from time to time and virtually every operating system must respond to floating-point exceptions such are overflow.

Q 14. List the functions of 8251.

(PTU, May 2012)

Ans. The functions of 8251 are:

- 1. 8251 can be used to transmit receive serial data. Data transmission to a CRT terminal using the 8251 in status check mode.

- 2. A programmable chip designed for synchronous/asychronous serial data communication.

Q 15. Perform the subtraction with the following assigned binary number by taking the (PTU, Dec. 2010) 2's complement of the subtrahend 11010-11111.

**Ans.** At Let X = 11010 and Y = 11111. So X - Y

Using 2's complement will be

X = 11010

2's complement of Y = 00001

Sum = 11011

Here no carry means, the X-Y will be negative 2's complement of sum above i.e. 00101.

Q 16. Where ASCII code is used in computers?

Ans. The American standard code for information interchange (ASCII) is a character-encoding scheme based on the ordering of the English alphabet. ASCII codes represent text in computers communications equipment and other devices that use text. Most modern character encoding schemes are based on ASCII though they support many more characters than ASCII does.

ASCII is the Internet Assigned Numbers Authority (IANA) preferred charset name for ASCII.

Q 17. An 8-bit register contains the binary value 10011100. What is the register value after (PTU, May 2011) arithmetic shift right?

Ans. 00010111 Right shift = 00001011

In this case, the rightmost 1 was shifted out a new 0 was copied into the leftmost portion, preserving the sign of the computer.

Q 18. Represent the following conditional control statement by two register transfer statements with the control functions.

If

$$(P = 1)$$

then  $(R_1 \leftarrow R_2)$  else if  $(Q = 1)$  then  $(R_1 \leftarrow R_3)$ .

(PTU, May 2011)

Ans.  $P: R_1 \leftarrow R_2$ ; if (P = 1) then  $(R_1 \leftarrow R_2)$

$P'Q: R_1 \leftarrow R_3$ ; Else if (Q = 1) then  $(R_1 \leftarrow R_3)$

Q 19. Write a symbolic microprogram for the ADD operation.

(PTU, May 2011)

Ans. The execution of the ADD instruction is carried out by the micro in structures at addresses

1 and 2. The first microstruction reads the operand from memory into DR. The second microinstruction performs and add micro-operation with the contact of DR and AC and then jumps back to the beginning of the getch routine.

| Lable   | Microoperations | , CD | BR          | AD       |

|---------|-----------------|------|-------------|----------|

| ADD:    | ORGO            | 1    | CALL        | Indirect |

| F       | NOP             | u    | JMP.        | - Next   |

| ' - " · | READ            |      | energy bar. |          |

| \ .     | ADD             | u i  | JUMP        | FETCH    |

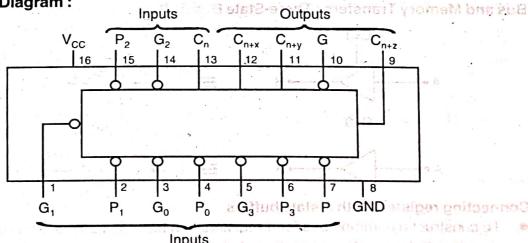

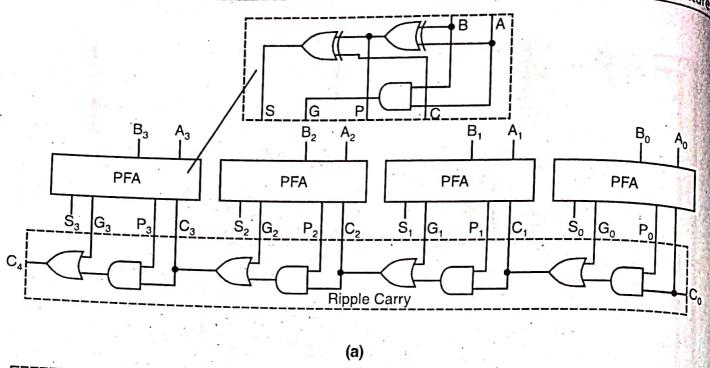

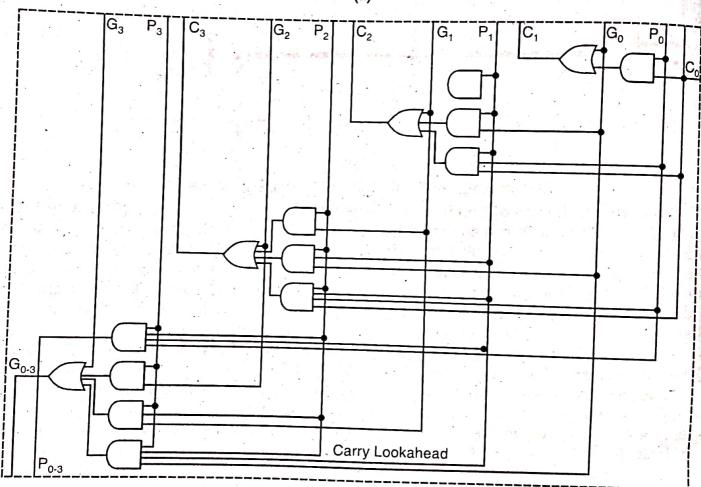

Q 20. With the help of circuits discuss look ahead carry generator. Show how it makes faster additions. (PTU, Dec. 2010)

Ans. These circuits are high-speed, look-ahead away generators, capable of anbicipating a carry across four binary adders or groups of adders. They are cascaded to perform full look ahead across n-bit adders. Carry-generate carry and propagate carry functions are provided as shown in the pin designation table.

When used in conjunction with the 181 arithmetic logic unit these generators provides high-speed carry look-ahead capability for any word length. Each DM74SI82 generators the look-ahead (anticipated carry) across a group of four ALU's and in addition, other carry look-ahead circuits may be employed to anticipate carry across sections of four look-ahead perform multi-level look-ahead is illustrated under typical application data.

Carry input and output of the ALU's are in their true formand the carry propagate (P) and carry generate (G) are in negated form therefore the carry functions (inputs, outputs, generate and propagate) of the look-ahead generators are implemented in the compatible forms for direct connection to the ALU reinterpretations of carry functions as explained on the 181 data sheed are also applicable to and compatible with the look-ahead generator positive logic equations for the DM748182 are:

$$\begin{array}{l} \text{Cn+x} = \overline{G}_0 + \overline{P}_0 \, C_n & \text{varied sists aunshed } \\ C_{n+y} = G_1 + \overline{P}_1 G_0 + \overline{P}_1 \overline{P}_0 \, C_n & \text{sevention as above be} \\ C_{n+z} = \overline{G}_2 + \overline{P}_2 \, \overline{G}_1 + \overline{P}_2 \, \overline{P}_1 \, \overline{G}_0 + \overline{P}_2 \, \overline{P}_1 \, \overline{P}_0 \, C_n & \text{sevention as above be} \\ = \overline{G}_3 \left( \overline{P}_3 + \overline{G}_2 \right) \left( \overline{P}_3 + \overline{P}_2 + \overline{G}_1 \right) \left( \overline{P}_3 + \overline{P}_2 + \overline{P}_1 + \overline{G}_0 \right) \\ \overline{P} = \overline{P}_3 \, \overline{P}_2 \, \overline{P}_1 \, \overline{P}_0 & \text{sevention as above be} \end{array}$$

**Connection Diagram:**

| Designation                                                       | Pin Nos     | Function                          |

|-------------------------------------------------------------------|-------------|-----------------------------------|

| G <sub>0</sub> , G <sub>1</sub> , G <sub>2</sub> , G <sub>3</sub> | 3, 1, 14, 5 | . Active Low Carry generate input |

| P <sub>0</sub> , P <sub>1</sub> , P <sub>2</sub> , P <sub>3</sub> | 4, 2, 15, 6 | Active low Carry propagate input  |

| Cn                                                                | 13          | Carry input                       |

| Cn+x, Cn+y                                                        | 12, 11, 9   | Carry outputs                     |

| Cn+2                                                              | - 8 - 88    |                                   |

| G                                                                 | 10          | Active low Carry propagate output |

| P                                                                 | 7           |                                   |

| V <sub>CE</sub>                                                   | 16          | Supply voltage                    |

| GND                                                               | 8           | Ground                            |

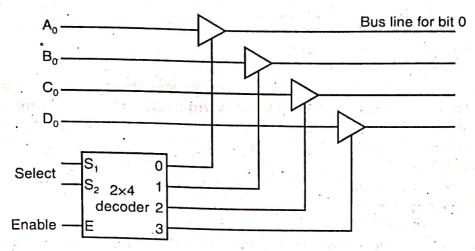

Q 21. Draw the diagram for a common bus system using tri-state buffers and a decoder instead of multiplexers. (PTU, May 2011)

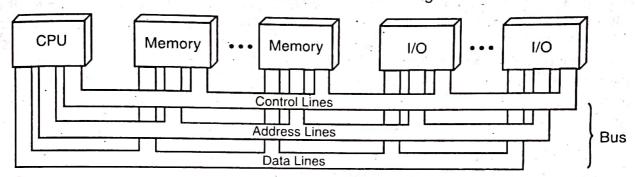

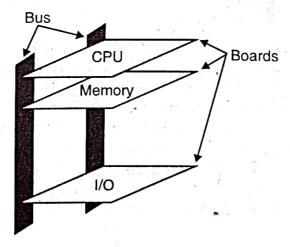

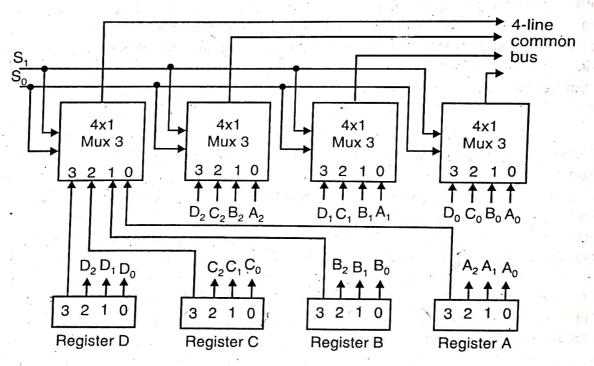

#### Ans. Bus transfers

- The transfer of information from a bus into one of many destination registers can be accomplished by connecting the bus lines to the inputs of all destination registers and activating the load control of the particular destination register selected.

- The symbolic statement for a bus transfer may mention the bus or its presence may be implied in the statement. When bus is included in the statement we write:

BUS ← C, R1 ← BUS (however it is R1 ← C)

#### Tri State Bus Buffers

- A three-state gate is a digital circuit that exhibits three states. Two of the states are signals

equivalent to logic 1 and 0 as in a conventional gate.

- The third state is called high impedance state

- The high impedance state behaves like an open circuit which means that the output is disconnected and does not have a logic significance.

#### Bus and Memory Transfers: Three-State Bus Buffers

#### Connecting registers with 3-state buffers

• To construct a common bus for 4 registers of n bits each using3-state buffers, we need n circuits with four buffers in each, as follows:

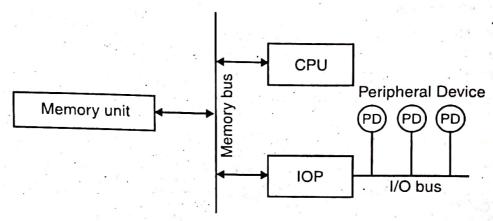

Q 22. Draw the block diagram of a computer and explain the function of each block.

(PTU, Dec. 2007; May 2016, 2004)

Ans.

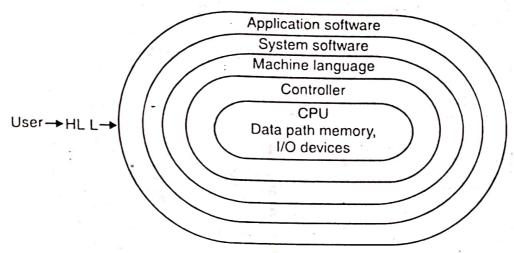

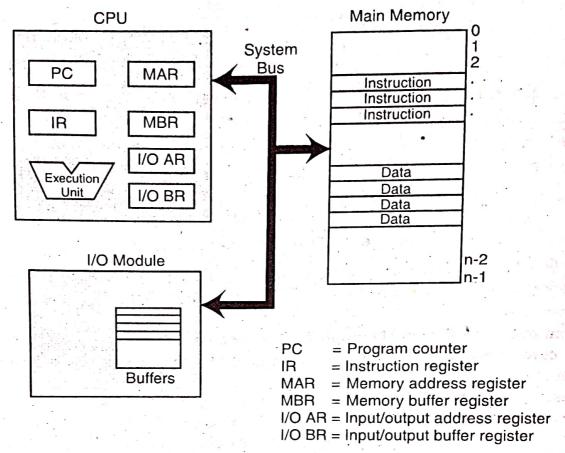

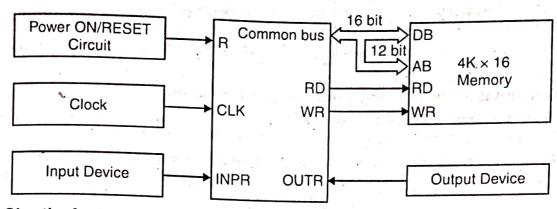

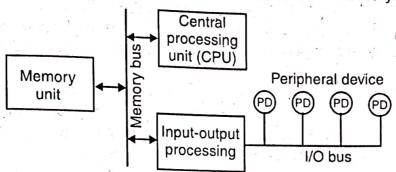

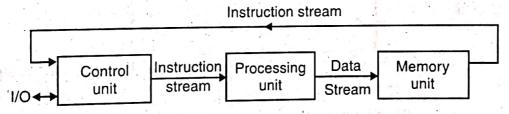

The block diagram of a computer is shown above. Basically, the hardware of computer is divided into three major parts.

- 1. CPU: CPU is Central Processing Unit and it contains an Arithmetic and logic unit for manipulating data, a number of registers for storing data, and control circuits for fetching and executing instructions.

- **2. Memory :** The memory of a computer consists of storage for instruction and data. Normally, it is called Random Access Memory (RAM) because CPU can access any location in memory at random and retrieve any information within a fixed interval to time.

The Input and Output processor/Job consists of electronic circuits and is used for communicating and controlling the transfer of information or between computer and outside world. i.e. it performs the basic input and output operations when CPU sends a request to it.

- **3. I/O Devices**: The input and output devices are peripheral input devices, such as keyboard, mouse, etc are used to input any data to the processor monitor, printer, etc are used result to the user which inputs the data.

- Q 23. Perform the subtraction with the following unsigned binary number by taking the 2's complement of the subtrahend 100-11000. (PTU, Dec. 2004)

**Ans.** Let x = 00100 and y = 11000

So x-y using 2' complement will be

x = 00100

2's complement of y = 01000

Sum = 01100

Here no carry means, the x-y will be -ve 2's complement of sum above i.e. 10100.

Q 24. Perform the subtraction with the following unsigned binary number by taking the 2's complement of the subtrahend 11010-11111. (PTU, May 2005)

**Ans.** Let x = 11010 and y = 11111. So x-y

Using 2's complement will be

x = 11010

2's complement of y = 00001

Sum = 11011

Here no carry means, the x-y will be negative 2's complement of sum above i.e. 00101.

Q 25. Perform the subtraction with the following unsigned binary number by taking the 2's compliment of the subtrahend 1010100-1010100. (PTU, Dec. 2009, 2005)

**Ans.** Let x = 1010100 and y = 1010100

So x - y using 2's complement will be.

x = 1010100

y = 0101100 (2's complement of y)

Sum = 10000000

Discarding the end carry then x - y = 000000

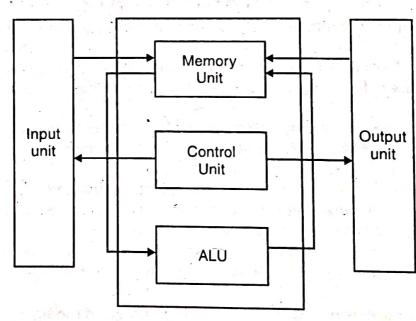

Q 26. Explain about the computer organization.

(PTU, Dec. 2006)

Ans. There are mainly five units is a computer organization:

- 1. Input Unit

- 2. Output Unit

- 3. Memory

- 4. Control Unit

- 5. Arithmetic and logic unit

**CPU**

**Block Diagram of Computer**

#### Q 27. Explain the meaning of the memory – reference instruction STA.

(PTU, Dec. 2009)

Ans. Memory reference instruction STA occupies memory address which is 8 bit number. Memory reference instruction STA occupy 2 consecutive bytes of RAM. The first byte is reserved for opcode and the second byte indicates the 8 bit memory address. STA instruction stores the accumulator to memory. The instruction STA 100 means "Store the value currently in the accumulator in memory address 100".

The following program illustrates how can translate the statement  $Z = A^*B + C^*D - E^*F$  into a sequence of one-address instructions :

| LDA  | Ε    | ;     | Acc <- E        |

|------|------|-------|-----------------|

| MUL  | F    | ;     | Acc <- Acc * F  |

| STÁ  | , T1 | ;     | T1 <- Acc       |

| LDA  | C    | - ; · | Acc <- C        |

| MUL  | D    | ;     | Acc <- Acc * D  |

| ST,A | T2   | ;     | T2 <- Acc       |

| LDA  | A    | ;     | Acc <- A        |

| MUL  | В    | ;     | Acc <- Acc * B  |

| ADD  | T2   | ;     | Acc <- Acc + T2 |

| SUB  | T1   | ;     | Acc <- Acc - T1 |

| STA  | Z    | ;     | Z <- Acc        |

|      |      |       |                 |

In this program, T1 and T2 represent the addresses of memory locations used to store temporary results. Instructions that do not require any addresses are called "zero-address instruction." All microprocessors include some zero-address instructions in the instruction set. Typical examples of zero-address instructions are CLC (clear carry) and NOP.

#### Q 28. Differentiate between arithmetic shift and logical shift.

(PTU, Dec. 2007)

Ans. The arithmetic instruction for logical operation are:

Clear, compliment, AND, OR, XOR, Clear and Carry, set array, complement carry, enable or disable interrupt.

The instructions for shift operation are:

- 1. Logical shift right

- 2. Logical shift left

- 3. Arithmetic shift right

- 4. Arithemetic shift left

- 5. Rotate right

- 6. Rotate left

- 7. Rotate right through carry

- 8. Rotate left through carry

**Shift Operation:** The circular shift operations are machine instructions in basic computer. The other shifts of interest are logic shift and arithmetic shifts. These two shifts can be programmed with a small number of instructions.

The logical shift requires that zeros to be added to extreme positions. This is easily accomplished by clearing E and circulating AC and E. Thus a logical shift right operation need two instruction:

CLE

CIR

For a logical shift left operation we need two instructions:

- -CLE

- -CIL

1.

2.

For a basic computer we have adopted signed 2's component representation:

# Arithmetic shift An arithmetic shift via micro operation that shifts a signed binary number to the left and right. An arithmetic shift left multiplies assigned binary number by. An arithmetic shift right

3. For example:

R1 ← Shift R1

divides number by 2.

R2 ← Shift R2

an micro operations that specify a 1-bit shift to left of content of register R1 and 1-bit shift to right of content of register R2.

- 4. The register symbol must be same on both sides of the arrow.

- The bit transferred to the end position through serial input is assumed to be 0 during a logical shift.

#### Logical shift

- A logical shift is one that transforms through the serial input.

- The symbols strand and for logical shift left and logical shift right microoperations.

- 3. For example:

The left most bit is a register that holds sign bit and remaining bits and remaining bits hold the number.

- It does not follow the conditions as followed by arithmetic shift micro operations.

- The bit is not transerred to the end position through serial input, since it follow difference arithmetic logic.

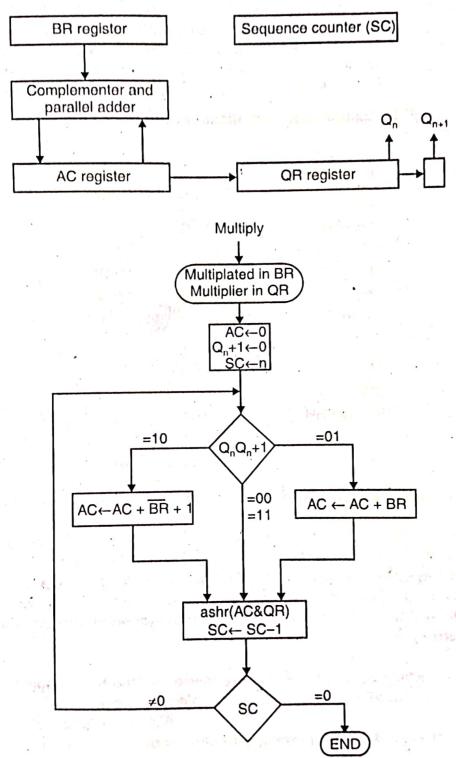

Q 29. Discuss Booth Multiplication algorithm with the help of suitable example.

(PTU, Dec. 2011, 2010, 2008; May 2005)

Ans. Booth Multiplication Algorithm: Booth algorithm gives a procedure for multiplying binary integers in signed-2's complement representation. It operates on the fact that strings of 0's in the multiplier require no addition but just shifting, and a string of 1's in the multiplier from bit weight  $2^k$  to weight  $2^{in}$  can be treated as  $2^{k+1}-2^m$ . For example, the binary number 001110 (+14) has a string of 1's from  $2^3$  to  $2^1$  (k=3, m=1). The number can be represented as  $2^{k+1}-2^m=2^4-2^1=16-2=14$ . Therefore, the multiplication  $M\times 14$ , where M is the multiplicand and 14 the multiplier, can be done as  $M\times 2^4-M\times 2^1$ . Thus the product can be obtained by shifting the binary multiplicand M four times to the left and subtracting M shifted left once.

As in all multiplication schemes, Booth algorithm requires examination of the multiplier bits and shifting of the partial product, Prior to the shifting, the multiplicand may be added to the partial product, subtracted from the partial product, or left unchanged according to the following rules:

- 1. The multiplicand is subtracted from the partial product upon encountering the first least significant 1 in a string of 1's in the multiplier.

- 2. The multiplicand is added to the partial product upon encountering the first 0 (provided that there was a previous 1) in a string of 0's in the multiplier.

- 3. The partial product does not change when the multiplier bit is identical to the previous multiplier bit.

The algorithm works for positive or negative multiplers in 2's complement representation. This is because a negative multiplier ends with a string of 1's and the last operation will be a subtraction of

the appropriate weight. For example, a multiplier equal to -14 is represented in 2's complement as 110010 and is treated as  $-2^4 + 2^2 - 2^1 = -14$ .

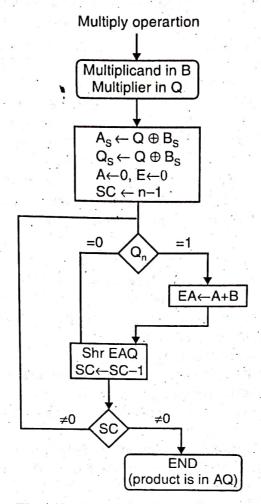

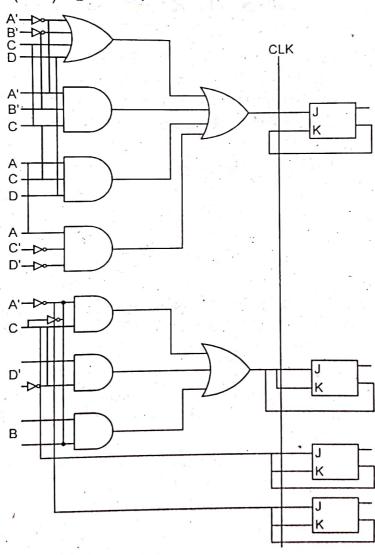

The hardware implementation of Booth algorithm requires the register configuration shown in Fig. This is similar to Fig. except that the sign bits are not separated from the rest of the registers. To show this difference, we rename registers A, B, and Q, as AC, BR, and QR, respectively.  $Q_n$  designates the least significant bit of the multiplier in register QR. An extra flip-flop  $Q_{n+1}$  is appended to QR to facilitate a double bit inspection of the multiplier. The flowchart for Booth algorithm is shown in Fig. AC and the appended bit  $Q_{n+1}$  are initially cleared to 0 and the sequence counter SC is set to a number n, equal to the number of bits in the multiplier.

The two bits of the multiplier in  $Q_n$  and  $Q_{n+1}$  are inspected. If the two bits are equal to  $10^{-1}$ means that the first 1 in a string of 1's has been encountered. This requires a subtraction of the multiplicand from the partial product in AC. If the two bits are equal to 01, it means that the first 0 in a string of 0's has been encountered. This requires the addition of the multiplicand to the partial product in AC. When the two bits are equal, the partial product does not change. An overflow cannot occur because the addition and subtraction of the multiplicand follow each other. As a consequence, the two numbers that are added always have opposite signs, a condition that excludes an overflow. The next step is to shift right the partial product and the multiplier (including bit  $Q_{n+1}$ ). This is an arithmetic shift right (ashr) operation which shifts AC and QR to the right and leaves the sign bit in AC unchanged (see Sec. 4-6). The sequence counter is decremented and the computational loop is repected n times

A numerical example of Booth algorithm is shown in Table for n = 5. It shows the step -by-step multiplication of  $(-9) \times (-13) = +117$ . Note that the multiplier in QR is negative and that the multiplicand in BR is also negative. The 10-bit product appears in AC and QR and is positive. The final value of  $Q_{n+1}$  is the original sign bit of the multiplier and should not be taken as part of the product.

TABLE: Example of Multiplication with Booth Algorithm

|       |                                      | maniphodilon | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | ,                |          |

|-------|--------------------------------------|--------------|-----------------------------------------|------------------|----------|

|       | BR = 10111                           | .*           |                                         |                  | To Table |

| $Q_n$ | $Q_{n+1} = \overline{BR} + 1 = 0100$ | 01 AC        | QR                                      | Q <sub>n+1</sub> | SC       |

|       | Initial                              | 00000        | 10011                                   | 0                | 101      |

|       | 0 Subtract BR                        | <u>01001</u> |                                         |                  |          |

| *     |                                      | 01001        |                                         |                  |          |

| · ·   | ashr                                 | 00100        | 11001                                   | _ 1 _ * "        | 100      |

| . 1   | 1 ashr                               | 00010        | 01100                                   | 1                | 011      |

| 0     | 1 Add BR                             | 10111        |                                         |                  |          |

|       |                                      | 11001        |                                         |                  |          |

|       | ashr                                 | 11100        | 10110                                   | 0                | 010      |

| 0     | 0 ashr                               | 11110        | 01011                                   | 0                | 001      |

|       | 0 Subtract BR                        | 01001        |                                         | <u>-</u>         | 001      |

|       |                                      | 00111        |                                         |                  | 7        |

|       | ashr                                 | 00011        | 10101                                   | 1 1              | 000      |

Q 30. What are the two instructions needed in the basic computer in order to set the E flip flop to 1?

Ans. Electronics a flip-flop or latch is a circuit that has two stable states and can be used to store state information. The circuit can be made to change state by signals applied to one or more control input and will have one two output flip-flop and latches are fundamental building block of digital electronics systems used in computers, communications and many other types of systems.

Q 31. Explain addition subtraction algorithm with signed magnitude data, also give the hardware implementation. (PTU, May 2007)

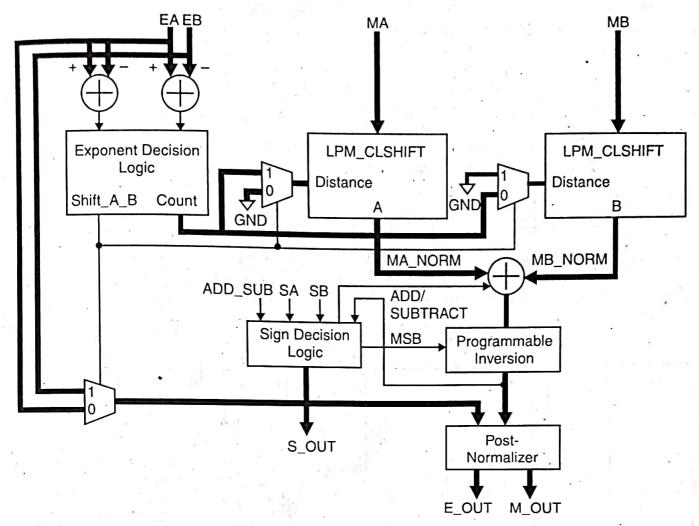

OR With the help of a flow chart discuss the process of subtraction of floating point numbers. Also explain the issues involved in its hardware implementation.

(PTU, May 2012, 2006; Dec. 2017, 2004)

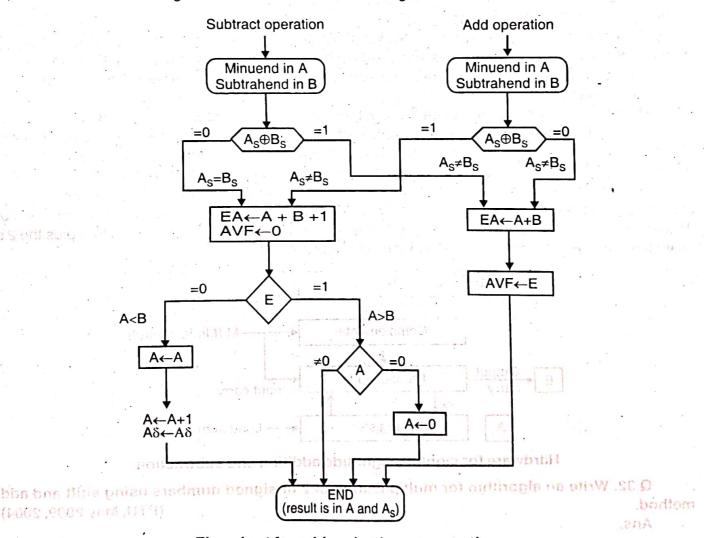

Ans. Flowchart for add and subtract operations: The flowchart for the hardware algorithm is

presented in Fig. The two signs A, and B, are compared by an exclusive- OR gate. If the output of the gate is O, the signs are identical; if it is I, the signs are different For an add operation, identical signs dicate that the magnitudes be added. For a subtract operation, different signs dicate that the magnitudes be added. The magnitudes are added with a microoperation  $EA \leftarrow A + B$ , where EA is a register that combines E and A. The carry in E after the addition constitutes an overflow if it is equal to 1. The value of E is transferred into the add-overflow flip-flop AVF.

The two magnitudes are subtracted if the signs are different for an add operation or identical for a subtract operation. The magnitudes are subtracted by adding A to the 2's complement of B. No overflow can occur if the numbers are subtracted so AVF is cleared to O. A 1 in E indicates that  $A \ge B$  and the number in A is the correct result, If this number is zero, the sign  $A_s$  must be made positive to avoid a negative zero. A O in E indicates that A < B. For this case it is necessary to take the 2's complement of the value in A. This operation can be done with one microoperation  $A \leftarrow \overline{A} + 1$ . However, we assume that the A register has circuits for microoperations complement and increment, so the 2's complement is obtained from these two microoperations. In other paths of the flowchart, the sign of the result is the same as the sign of A, so no change in A, is required. However, when A < B, the sign of the result is the complement of the original sign of A. It is then necessary to complement A, to obtain the correct sign. The final result is found in register A.

Flowchart for add and subtract operations

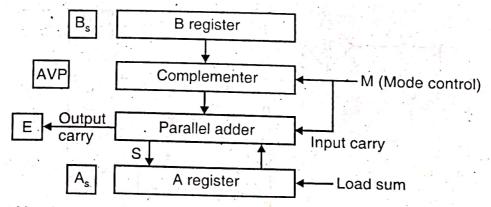

Hardware Implementation: To implement the two arithmetic operation with hardware, it is first necessary that the two numbers be stored in registers. Let A and B be two registers that hold the corresponding signs magnitudes of the numbers, and A<sub>S</sub> and B<sub>S</sub> be two flip-flop that hold the corresponding signs. The result of the operation may be transferred to a third register: however, a saving is achieved if the result of the operation may be transferred to a third register: is transferred into A and  $A_{\rm S}$ . Thus A and  $A_{\rm S}$  together form an accumulator register.

Consider now the hardware implementation of the algorithms above. First, a parallel-adder is needed to perform the microopoeration A + B. Second, a comparator cricuit is needed to establish if A > B, A = B, or A < B. Third, two parallel-subtractor circuits are needed to perform the microoperations A > B, A = B, or A < B. Third, two parallel-subtractor of solid S. S. A = B and B - A. The sign relationship can be determined from an exclusive OR gate with A<sub>S</sub> and B<sub>S</sub>

This procedure requires a magnitude comparator, an adder, and two subtractors. However, a different procedure can be found that required less equipment. First, we know that subtraction can be accomplished by means of complement and add. Second, the result of a comparison can be determined from the end carry after the subtraction. Careful investigation of the alternatives reveals that the use of 2's complement for subtraction and comparison is an efficient procedure that requires only an adder and a complementer.

Fig. shows a block diagram of the hardware of the hardware for implementing the addition and substraction operations. It consists of registers A and B and sign flip-flop A<sub>S</sub> and B<sub>S</sub>. Subtraction is done by adding A to the 2's complement of B.

The output carry is transferred to flip-flop E, where it can be checked to determine the relative magnitudes of the two numbers. The add-overflow flip-flop. AVF holds the overflow bit when A and B are added. The A register provides other microoperations that may be needed when we specify the sequence of steps in the algorithm.

The addition of A plus B is done through the parallel adder. The S (sum) output of the adder is applied to the input of the A register. The complementer provides an output of B or the complement of B depending on the state of the mode control M. The complement consists of exclusive-OR gates and the parallel adder consists of full-adder circuits as shown in Fig. in Chap 4. The M signal is also applied to the input carry of the adder. When M = 0, the output of B is transferred to the adder, the input carry is 0, and the output of the adder is equal to the sum A + B. When M = 1, the 1's complement of B is applied to the adder, the input carry is 1, and output S = A + B + 1. This is equal to A plus the 2's complement of B, which is equivalent to the subtraction A - B.

Hardware for signed magnitude addition and subtraction

Q 32. Write an algorithm for multiplication of 2 unsigned numbers using shift and add method. (PTU, May 2009, 2004)

Ans.

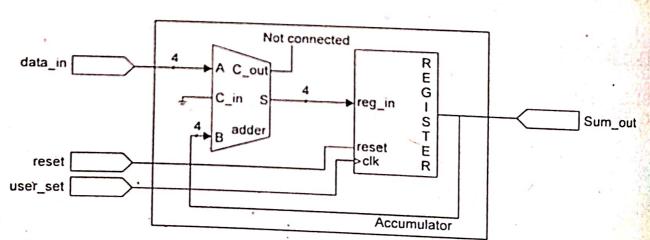

Initially, multiplicand is in register B and multiplier in Q. The sum of A and B forms a portial product which is transferred to the EA register. Both partial product and multiplier are shifted to right. The sequence counter SC is initially set to a no equal to no of bits in multiplier. The counter is decremental by 1 after forming each partial product. When content of counter reaches zero, the product is formed and process stops. The best significant bit of A is shifted into the most significant position if g. the of bit from E is shifted to MS most significant position of A and O is shifted into 'E'.

| , E, , | Α            | Cs           | SC            |

|--------|--------------|--------------|---------------|

| . 0    | 00000        | 10011        | . 101         |

|        | <u>10111</u> |              |               |

| 0      | 10111        | ·            |               |

| 0٠     | 01011        | 11001        | 100           |

|        |              | <u>10111</u> |               |

| 1      | 00010        |              | 43            |

| Q - 0  | 10001        | 01100        | 011           |

| 0      | 01000        | 10110        | 010           |

| 0      | 00100        | 01011        | 001           |

|        | <u>10111</u> |              |               |

| 0      | 11011        |              |               |

| 0      | 01101        | 10101        | 000           |

|        |              | ÷ 9          |               |

|        | 0<br>0<br>0  | 0 00000      | 0 00000 10011 |

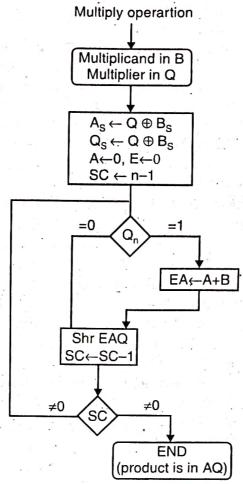

Q 33. Write an Algorithm of multiplication.

Ans. Algorithm of Multiplication.

(PTU, Dec. 2006)

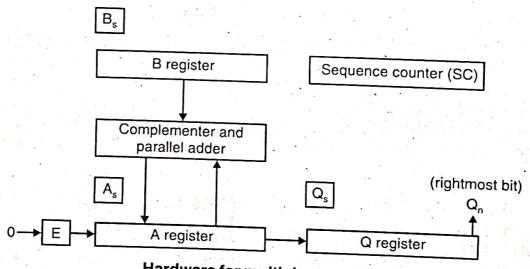

Hardware Implementation for Signed-Magnitude Data: When multiplication is implemented in a digital computer, it is convenient to change the process slightly. First, instead of providing registers to store and add simultaneously as many binary numbers as there are bits in the multiplier. it is convenient to provide an adder for the summation of only two binary numbers and successively accumulate the partial products in a register. Second, instead of shifting the multiplic and to the left, the partial product is shifted to the right, which results in leaving the partial product and the multiplicand in the required relative positions. Third, when the corresponding bit of the multiplier is 0, there is no need to add all zeros to the partial product since it will not alter its value.

The hardware for multiplication consists of the equipment shown in Fig. plus two more registers. These registers together with registers A and B are shown in Fig. The multiplier is stored in the Q register and its sign in  $Q_s$ . The sequence counter SC is intially set to a number equal to the number of bits in the multiplier. The counter is decremented by I after forming each partial product. When the content of the counter reaches zero, the product is formed and the process stops.

Initially, the multiplicand is in register B and the multiplier in Q. The sum of A and B forms a partial product which is transferred to the EA register. Both partial product and multiplier are shifted to the right. This shift will be denoted by the statement shr EAQ to designate the right shift depicted in Fig. The least significant bit of A is shifed into the most significant position of Q, the bit from E is shifted into the most significant position of A, and 0 is shifted into E. After the shift, one bit of the partial product is shifted into Q, pushing the multiplier bits one position to the right. In this manner, the rightmost flip-flop in register Q, designated by Q<sub>n</sub>, will hold the bit of the multiplier, which must be

Hardware for multiply operation

Hardware Algorithm: Fig. is a flowchart of the hardware multiply algorithm. Initially, the multiplicand is in B and the multiplier in Q. Their corresponding signs are in B, and Q<sub>s</sub>,respectively. The signs are compared, and both A and Q are set to correspond to the sign of the product since a double-length product will be stored in registers A and Q. Registers A and E are cleared and the sequence counter SC is set to a number equal to the number of bits of the multiplier. We are assuming here that operands are transferred to registers from a memory unit that has words of a bits. Since an operand must be stored with its sign, one bit of the word will be occupied by the sign and the magnitude

#### Flowchart for multiply operation

After the initialization, the low-order bit of the multiplier in  $Q_n$  is tested. If it is a 1, the multiplicand in B is added to the present partial product in A. If it is a 0, nothing is done. Register EAQ is then shifted once to the right to form the new partial product. The sequence counter is decremented by 1 and its new value checked. If it is not equal to zero, the process is repeated and a new partial product is formed. The process stops when SC = 0. Note that the partial product formed in A is shifted into Q one bit at a time and eventually replaces the multiplier. The final product is available in both A and Q, with A holding the most significant bits and Q holding the least significant bits.

# Q 34. What are the various issues for designing the instruction set of a processor? (PTU, May 2009)

Ans. Instruction Set: An instruction set, or instruction set architecture (ISA), is the part of the computer architecture related to programming, including the native data types, instructions, registers, addressing modes, memory architecture, interrupt and exception handling, and external I/O. An ISA includes a specification of the set of opcodes (machine language), and the native commands implemented by a particular processor.

Instruction set architecture is distinguished from the microarchitecture, which is the set of processor design techniques used to implement the instruction set. Computers with different microarchitectures can share a common instruction set. For example, the Intel Pentium and the AMD Athlon implement nearly identical versions of the x86 instruction set, but have radically different internal designs.

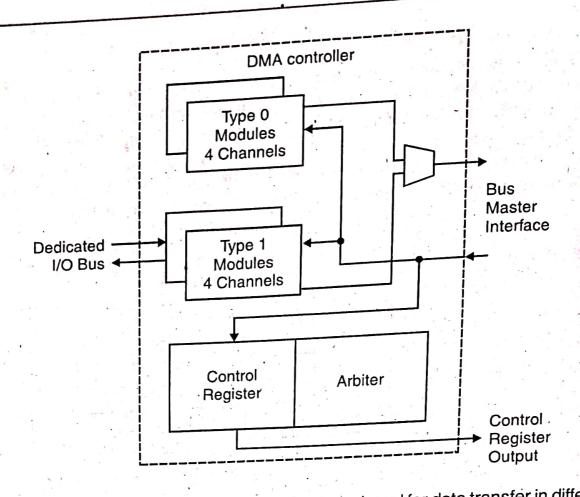

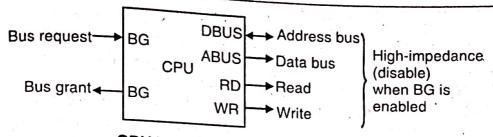

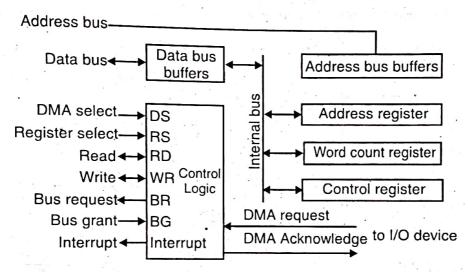

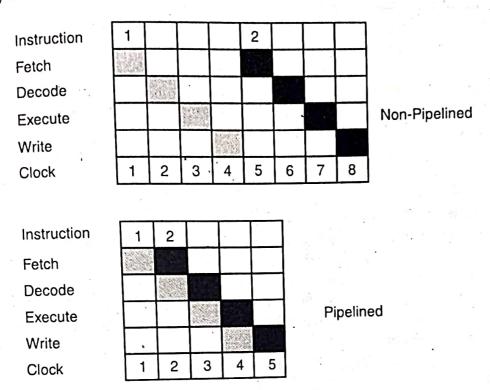

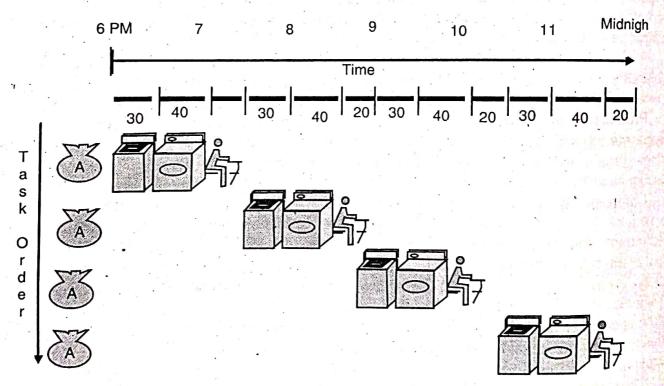

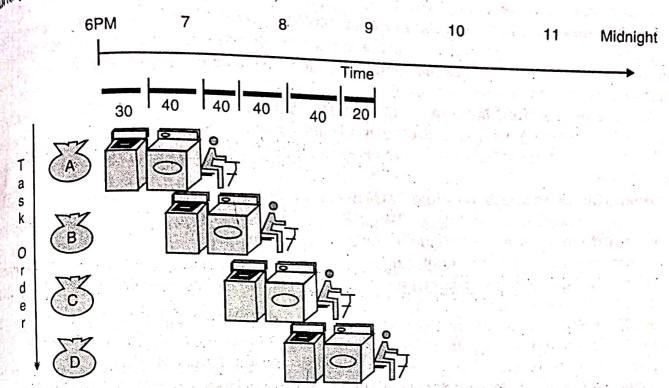

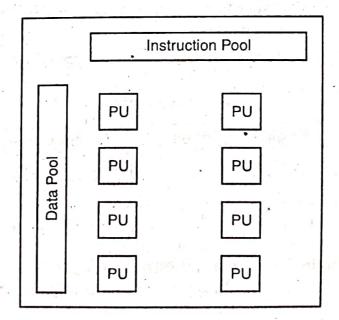

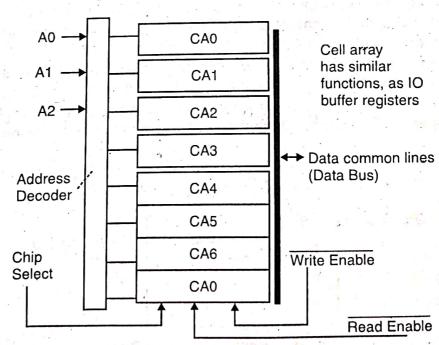

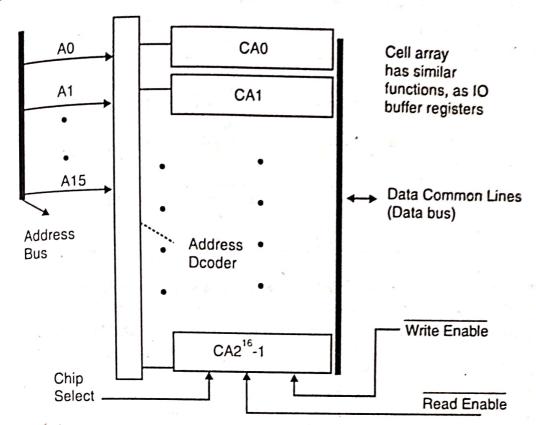

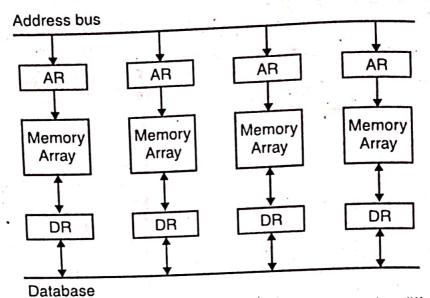

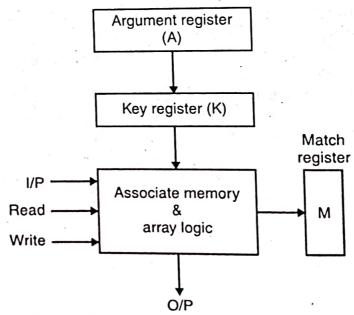

This concept can be extended to unique ISAs like TIMI (Technology-Independent Machine